FPGA算法技术交流问答集锦(5.21~5.28)

本次整理2023年5月21日~28日,FPGA技术交流群的相关问答。相关问题的解答和交流来自群成员,仅作参考。 一、DDR3存储相关 1. &nb

本次整理2023年5月21日~28日,FPGA技术交流群的相关问答。相关问题的解答和交流来自群成员,仅作参考。

一、DDR3存储相关

1. 大家操作DDR,都是用AXI4吗,还是自己写控制器?

答:App和AXI4都用过,现在以AXI4为主。

2. 没用Block Design,怎么知道DDR3的起始地址?

答:

①起始地址在代码里自己写,在不用BD下,地址空间起止可自定义,DDR存储空间可以根据实际存储情况划分。默认起始地址为0。

②如果是是在BD中设计,可根据GUI的地址分配,设置地址的起止。

3. 美光公司被查未通过审核,利好国产存储,底气更足。

二、Ethernet相关

1. 手里的开发板有个光口,是不是可以再搞个万兆网卡,插PC上,可以进行通讯?

答:可以。方案:FPGA侧,用10G PHY 10G MAC。

三、时序约束相关

1. 请教一下,Vivado中,在用set_false path时,不生效,有解决方法吗?

答:

①应该是没设置好有效路径,有些信号可能扇出比较多,它实际的路径名字,跟时序分析窗口中的是不一致的,需要打开到最底层的路径,找到实际路径名。打开综合后的网表,找一下实际信号名字,看看跟时序窗口里的是否对应。或者把XDC的约束指令,通过Tcl Comsole界面敲一下,看看是否正确,一般不起效的约束,会报无效告警。

②格式错误,会报warning。

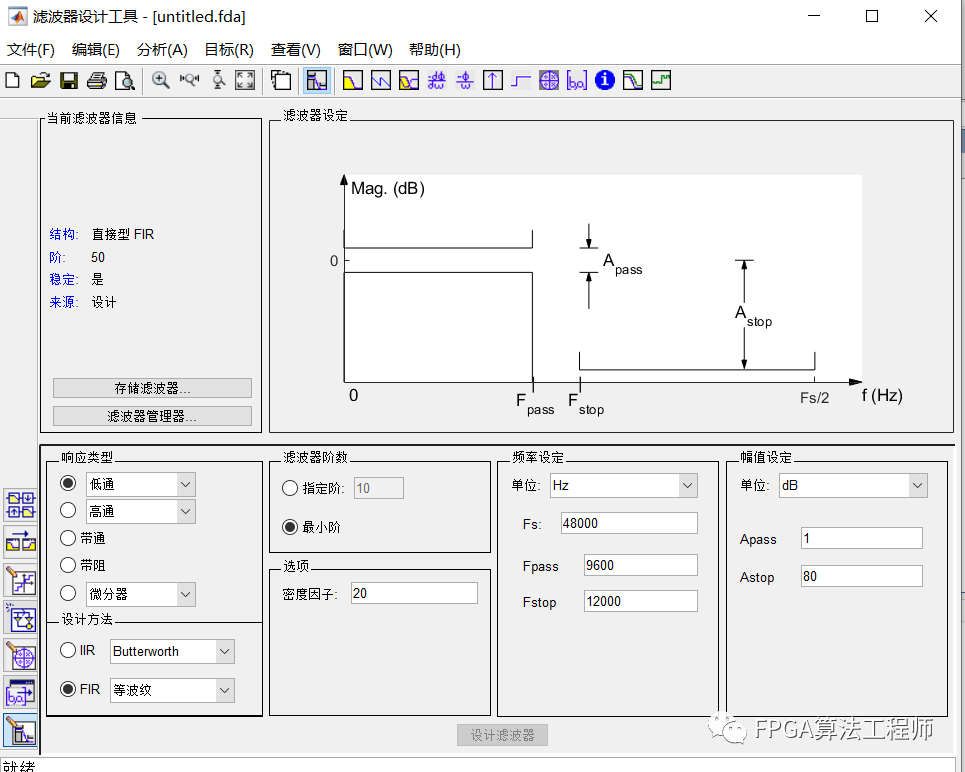

四、滤波器设计相关

1. 问一下,滤波器的阶数一般设置为多少,怎么确定阶数的大小?

答:

A. 没有一般,看你的工作参数和抑制效果,以性能为根本,实现时需要多少阶,取决于工作参数。比如:时钟速率,信号带宽,截止频率,抑制比。关键在于如何设计全链路参数,平衡性能和资源消耗。

B. 根据滤波器的带内纹波和带外衰减,用MATLAB仿真一下,看大概需要多少阶,需要结合FPGA的乘法器资源消耗。

C. 通带宽度,通带纹波,阻带衰减,过渡带宽度,相频特性,FIR还是IIR,资源消耗,都需要考量。

D. 对FPGA工程师来说,了解一些滤波器基础就够了,算法工程师设计滤波器需要深入研究。同样的需求,不同的算法工程师设计出的资源需求差别很大。

E. MATLAB中,常用filterDesigner进行滤波器设计评估。

F. 数字信号处理课程呼之欲出,后半部分全是滤波器设计,前半部分信号频谱分析。

G. MATLAB自带文档和示例,可能比书上写的更有用,不少工程的实现技巧,书上根本不会讲。大部分书讲理论,对于工程化,教授们望而却步。MATLAB的文档、理论和代码实现,都讲得很清楚,代码质量较高。

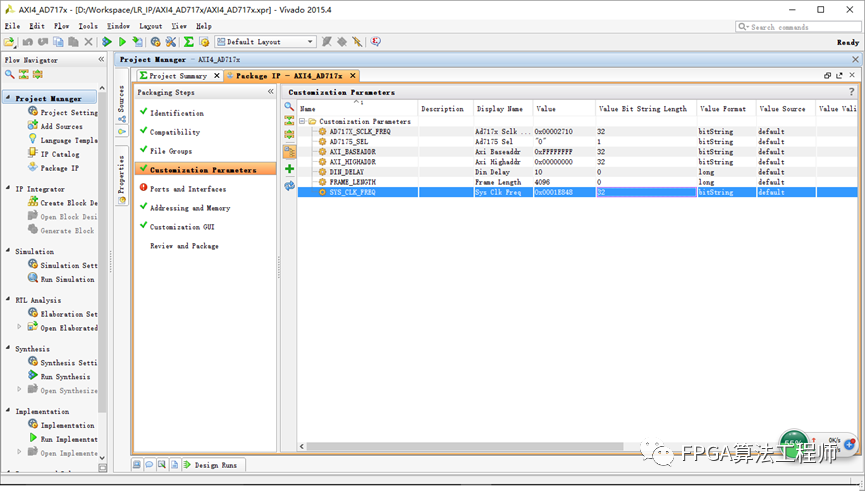

五、IP配置设计相关

1. 在Vivado IP配置界面中,配置的一些选项参数,是怎么被记录下来,然后传递到.v文件里面去的?

答:Vivado工具IP集成功能,就像自定义一个IP,可以定义配置参数,在IP生成时,会创建参数配置列表,传递到工程中。

六、FPGA前景相关

1. 能不能下个结论,现阶段FPGA是最辉煌的时候?

答:

A. FPGA的便捷性使得应用广泛,低、中、高系列器件,覆盖众多应用领域,从半导体发展历程来看,FPGA依然是不可或缺的重要领域。

B. 现在有很多FPGA和IC设计交流群,B站有部分不懂FPGA的UP主为了流量蹭热点,普及一下FPGA也是好事。

七、RFSoC器件相关交流

1.据说星链的部分系统,使用了Xilinx的RFSoC,相控阵,5G、卫星等使用较多。

2.据说国内某公司已经推出了RFSoC,好像是双DIE胶水的。

3.希望国内的正向和反向设计都抓紧研究,满足应用需求。

4.RFSoC的难点,在于ADC/DAC,省掉204B,节省功耗,集成度更高,高带宽和低延时。

5.RFSoC适合电子战等系统。

6.需要加强总体设计,好钢做好刀。

八、无线系统设计相关

1. 在无线电通信中,发射端和接收端的FPGA代码都写完了,但是通信没有成功。因此,想先调试发射端,有啥仪器可以用来调试发射端?答:

A. 先不用天线,用线缆和衰减器连接发射机和接收机,看看是啥效果。发射机发信号,用示波器和频谱仪看看波形频谱。

B. 发射端射频线街道矢量信号分析仪上,看频谱,可以基带I、Q信号解出来,也可以看星座图,分析EVM、相偏等。

C. 建议发射端、接收端、基带和射频,分开调试,便于问题定位。

九、ILA调试相关

1. 关于ILA时钟问题,ILA的时钟是PS端配置外部芯片产生的,如果是外部时钟还没配置完成,导致没有时钟,那等PS配置完,ILA不是应该能正常使用了吗?

答:不一定,ILA要求上电就有时钟。

2. 有啥方法能先配置完再启动PL吗?

答:Debug时钟进ILA之前加一个PLL;等PS配置时钟完成后,再用JTAG下载到PL。

3. 为啥Inout信号前面不能加keep true,加了之后输入抓到的全是0,不加就是正常的?

答:IO信号一般不会被优化掉,并且不能直接把IO信号拉到ILA中看。

十、FPGA在基站上的应用

FPGA的应用领域很多,做基站是其中一种。

做基站,用进口的FPGA还是国产的FPGA,取决于供应链和市场需求。

小公司,很难做好基站。

十一、FPGA贴片问题

1. 某型ZU系列FPGA贴片xx套,有多套出现故障,可能是什么原因导致的?

答:工艺、焊接(虚焊)、温度、PCB封装、短路等。建议先小批量投板、贴片验证测试。

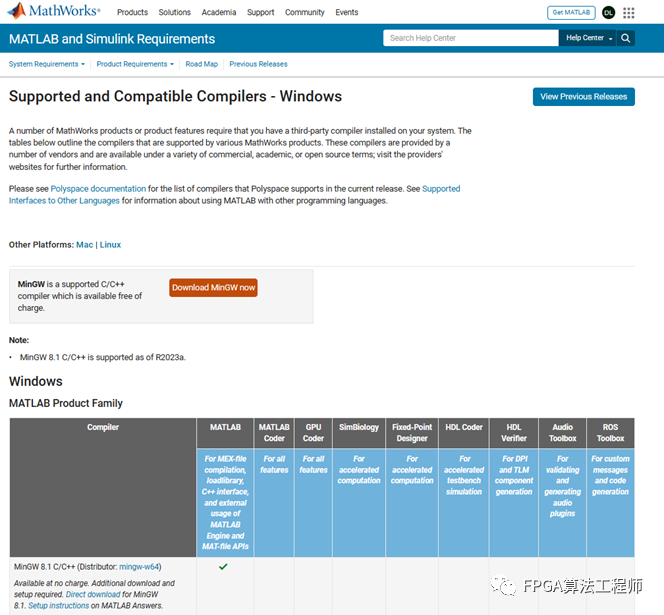

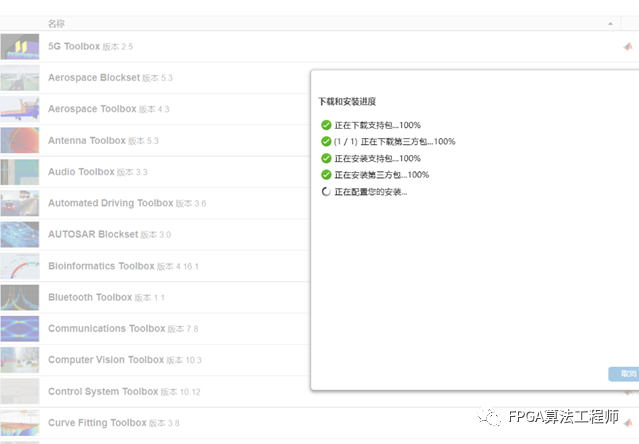

十二、MATLABMinGW64支持包安装相关

1. MATLAB程序中,可能会调用C/C++的程序,需要识别mex文件,相关解决方案如下:

在Mathworks官网下载MinGW支持包安装插件,mingw.mlpkginstall,然后在MATLAB打开,根据提示安装。

--<完>--

原文标题 : FPGA算法技术交流问答集锦(5.21~5.28)